Приведен перевод статьи Пауля Диллина об особенностях проектирования SDR радиостанций. Рассмотрено развитие SDR радиостанций, различные подходы проектирования, особенности применения различных технологий программируемых матриц и возникающие проблемы. Описаны пути использования Arria 10, приведены структурные схемы реализации.

Введение

В течение последнего десятилетия инженеры, работающие над созданием программно-определяемых радиосистем (SDR радиостанций), обнаружили, что разработка очень гибкой беспроводной системы, отвечающей требованиям военных к объему, весу и мощности (SWaP) по доступной цене, является сложной задачей.

Сектор SDR радиостанций получил большой импульс развития, когда в 1997 году была начата в США программа разработки перепрограммируемых тактических радиостанций, использующих единую архитектуру связи (JTRS радиостанций). Амбициозная цель программы заключалась в том, чтобы позволить мобильным сетям ad hoc связать воедино разрозненные беспроводные системы различных родов войск, других вооруженных сил НАТО, существующие радиостанции и некоторые гражданские системы. Эти системы включают наземные мобильные радиостанции (GMR), наземную и спутниковую связь.

Спецификация JTRS радиостанций характеризуется широким диапазоном так называемых "форм волны", которые могут модулироваться на любой радиочастоте (RF) в очень широком диапазоне от высоких (HF) до сверхвысоких (UHF) частот.

Физический уровень требований включает в себя ортогональное мультиплексирование с частотным делением (OFDM) и широкополосные технологии многократного доступа с кодовым делением (WCDMA), позволяющие пользователям общаться посредством голоса, данных и видео одновременно на всех уровнях безопасности.

Система была разработана с учетом потребности в мобильном командовании, управлении, связи, в компьютерах, разведке и наблюдении (C4ISR), а также в поддержании связи в хаотичной обстановке на поле боя с помощью самовосстанавливающейся сети.

Эти технологии требовали сложной обработки сигнала в базовом диапазоне частот для реализации различных форм волн. Для достижения как скорости обработки, так и низкого энергопотребления, конструкция требует некоторого аппаратного ускорения.

Двумя наиболее подходящими вариантами могут быть применение матриц жестко запрограммированных логических элементов или полевой программируемой логики, например, программируемых пользователем матриц логических элементов (FPGA).

К преимуществам "классически" запрограммированных матриц относятся оптимальная производительность и низкое их энергопотребление. Однако, как только в конструкции применен кремний, он обеспечивает постоянно фиксированную функциональность. Кроме того, в связи с длительными сроками производства, характерными для оборонных закупок, для передовых технологий резко возросли единовременные затраты на проектирование (NRE). Использование ПЛИС обеспечивает гибкую логическую структуру; благодаря возможности перепрограммирования, она позволяет тестировать конструктивные итерации на аппаратном уровне без NRE.

Радиочастотные проблемы, возникающие в процессе разработки, также оказались очень сложными Разработка радиочастотного канала, который может охватывать широкий диапазон частот, далеко не простая задача, особенно учитывая различные частоты, требующие настройки компонентов и гибкой антенны. Кроме того, полоса пропускания, необходимая для передачи голоса, намного меньше, чем та, которая требуется для передачи видео, что придает разработке дополнительную сложность. Быстрая скачкообразная перестройка частоты, расширенный спектр или OFDM, еще больше усугубляет проблемы.

К сожалению, требования оказалась слишком сложными и трудными для технологии времени начала разработки, и программа JTRS была окончательно отменена в конце 2011 года. В течение 15 лет разработки программа также страдала от недостатка функциональности и раздутых заказчиком требований, что сделало большую часть ранних работ устаревшими. Когда было объявлено об отмене программы, заместитель министра обороны процитировал: "По нашей оценке, маловероятно, что продукты, полученные в результате программы разработки JTRS GMR, будут по доступным ценам отвечать сервисным требованиям и могут вообще не соответствовать некоторым требованиям. Поэтому завершение программы необходимо".

Но программные элементы JTRS продолжали жить вплоть до 2014 года. Многие элементы программы JTRS остаются актуальными и сегодня.

Развитие закона Мура (удвоение числа используемых транзисторов раз в два года) неустанно продолжалось и привело к тому, что FPGA, изготовляемые ранее с использованием 20-нм планарной технологии, в настоящее время начинают поставляться с 14-нм новой Tri-Gate (или иначе FinFET) технологией. Это значительно повысило как сложность, так и производительность изготавливаемых цифровых матриц. Например, среднечастотное семейство Altera Arria 10 SX расширяется до 660k логических элементов, наряду с более чем 40 Мбит внутрисхемной оперативной памятью и более чем 1k DSP-ускорителями. 20-нм устройства SX также оснащены двумя высокопроизводительными ARM-процессорами.

Как дизайнер может использовать устройство Arria 10, чтобы соответствовать требованиям к базовой полосе SDR радиостанций?

Первое решение - разделить задачи между программным обеспечением, работающим на процессорах ARM, аппаратными ускорителями и интерфейсами, которые будут встроены в логическую структуру. Общее правило заключается в том, что вычислительные функции, такие как кодирование и декодирование при быстром преобразовании Фурье (БПФ) или Форвардное исправление ошибок (ФИК), обычно более эффективны в аппаратном обеспечении. Процессор идеально подходит для таких действий, как перемещение данных в память, проверка и манипулирование протоколами.

Эквивалентом полосы частот "форм волн" будут различные стандарты модуляции. Это может быть OFDM, требующий сложных БПФ вычислений, или мультидоступ с разделением кода (CDMA), требующий быстрой генерации расширяемого кода и корреляторов для распространения и восстановления получаемых данных.

Блоки DSP в устройстве Arria образуют ключевой элемент аппаратного ускорителя. Современные системы модуляции используют данные в виде In-phase (I) и Quadrature (Q) битпотоков, что позволяет модулировать несущую РЧ с квадратурной амплитудной модуляцией (QAM), например, 16 (до 256 QAM), или более простой квадратурной фазовой манипуляцией (QPSK). Эта важная высокопроизводительная задача может быть реализована в DSP и логической матрице для экономии общей мощности системы.

Новейший стандарт называется Multiple-Input Multiple-Output (MIMO), сложная схема, использующая две или более антенны, разделенные физическим расстоянием. Технологии MIMO улучшают спектральную эффективность и достигают увеличения коэффициента усиления при разнесенном приеме, что повышает надежность соединения в канале связи. Ожидается, что MIMO станет важным дополнением для удовлетворения растущего спроса на пропускную способность данных.

Программируемое логическое решение дает значительные дополнительные преимущества. Логическая функция определяется конфигурационным файлом, который хранится в энергонезависимой внешней памяти и загружается в устройство при включении; в памяти также хранится исполняемый код для ARM ядер. Это решение позволяет обновлять функциональность с помощью обновления программного обеспечения промежуточного периода, благодаря чему пользователи могут, например, поддерживать новые волновые формы в памяти или добавлять новые функции в ARM-код.

Процессоры ARM могут управлять потоком данных в ядра ПЛИС, используя их в качестве специально настроенных периферийных устройств.

В качестве примера можно выделить одно ядро для управления такими интерфейсами, как экран дисплея или видео экрана, одновременно проверяя достоверность полученных пакетов данных (см. Рисунок 1). Второй процессор может управлять аппаратными ускорителями, построенными на логических и DSP ресурсах. ARM может выбирать аппаратные ускорители, реализующие алгоритм, необходимый в настоящее время, например, для производства QAM16, а также для регулирования передачи данных в и из полевой программируемой радиочастотной микросхемы (FPRF).

Рисунок 1. ПЛИС, управляющая логикой SDR.

ARM может управлять устройством FPRF, используя простой и быстрый SPI интерфейс с помощью двухбайтовой инструкции, дающей ему полный контроль над радиочастотным доменом. Процессор также может обрабатывать сигнал индикатора уровня принимаемого сигнала (RSSI), показывающий уровень активности на выбранной частоте. Сочетание устройств FPGA и FPRF обеспечивает высокую гибкость, низкое энергопотребление и, прежде всего, экономичное решение для логических и RF областей применения.

LMS7002M, второе поколение FPRF

LMS7002M, второе поколение FPRF-устройств от компании Lime Microsystems, представляет собой недавно анонсированный 65-нм КМОП-чип с архитектурой сдвоенного приемопередатчика. Диапазон частот был расширен и теперь он охватывает от 50 МГц до 3800 МГц, обеспечивая поддержку низких частот, часто используемых в устаревших военных радиостанциях. Кроме того, верхний предел может быть легко расширен добавлением внешнего PLL и смесителя, что позволит охватить частоты, используемые в спутниковой связи.

LMS7002M включает в себя встроенный микроконтроллер; что упрощает калибровку микросхемы, которая в противном случае была бы сопряжена со сложными взаимодействиями с базовой логикой. Он калибрует смещение постоянного тока, настройку полосы пропускания фильтров нижних частот (LPF) трактов передачи/приема (TX/RX), передачу данных о местах повреждения локальных осцилляторов, определение коэффициентов усиления IQ и фазового рассогласования в цепях передачи и приема, а также выполняет калибровку чипового резистора и конденсаторов.

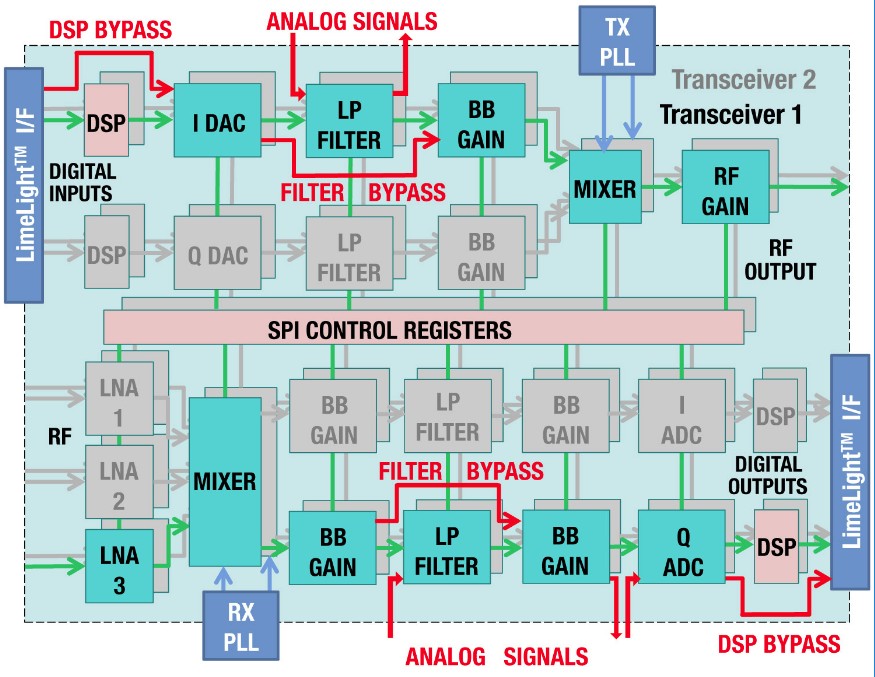

В большинстве случаев достаточно начальной калибровки, однако для военных беспроводных систем, работающих при экстремальных температурах и частотах, можно поручить микроконтроллеру провести повторную калибровку для обеспечения оптимальной производительности оборудования. Энергосберегающие функции включают в себя возможность выборочного отключения питания любого блока, когда он не требуется, с сохранением настроек и калибровки при сохранении питания памяти SPI интерфейса (см. Рисунок 2). Чип полевой программируемой радиочастотной микросхемы (FPRF-чип) размещается в корпусе размером 11,5 мм x 11,5 мм.

Рисунок 2. Каждый блок FPRF можно выборочно отключить или обойти.

Для помощи проектировщикам доступны различные инструменты, предоставляемые либо поставщиком ПЛИС, либо сторонними поставщиками. Например, Altera является единственным поставщиком FPGA, который предлагает общедоступный набор для разработки программного обеспечения, соответствующего стандарту Open Computing Language (OpenCL).

OpenCL позволяет программистам взять код и быстро использовать массивно параллельную архитектуру FPGA. Это позволяет эмулировать и отлаживать код ядра, выявлять узкие места в работе, а также создавать профили и перекомпилировать его в аппаратную реализацию.

Инструмент проектирования FPRF от компании Lime Microsystems имеет форму графического интерфейса пользователя (GUI); графический интерфейс доступен бесплатно и позволяет полностью контролировать устройство.

В течение последних двух лет автор статьи-источника Пауль Диллин работал с Lime Microsystems по ряду маркетинговых проектов. Ранее он 15 лет работал в отрасли FPGA и является автором отчета "Рынок FPGA". Пауль работал на стратегических и тактических маркетинговых должностях в ведущих американских и британских полупроводниковых компаниях и специализируется на конкурентном анализе и переговорах. Читатели могут связаться с ним по адресу paul@high-tech-marketing.co.uk.

Источники информации

1 Flexible military radios balance SWaP, cost specs, October 03, 2014. [Электронный ресурс]. URL: https://militaryembedded.com/comms/sdr/flexible-military-radios-balance-swap-cost-specs (Дата обращения: 24.07.2020).

0 коммент.:

Отправить комментарий